**WORKSHOP ON IC ADVANCES IN CHINA**

| CONTENT               | 目录       |

|-----------------------|----------|

|                       |          |

| ORGANIZERS & SPONSORS |          |

| 主办单位与支持单位             | Page 02  |

|                       |          |

| CONFERENCE COMMITTEE  |          |

| 会议组委会                 | Page 03  |

| CONFEDENCE VENUE      |          |

| CONFERENCE VENUE      | Da 04    |

| 会议地点                  | Page 04  |

| PROGRAM AT A GLANCE   |          |

| 会议日程概览                | Page 05  |

|                       |          |

| CONFERENCE SCHEDULE   |          |

| 会议日程详情                | Page 08  |

|                       |          |

| PLENARY TALK          |          |

| 大会报告                  | Page 22  |

| TUTORIAL              |          |

| 芯片设计培训班               | Page 25  |

|                       | i uge 13 |

| INVITED TALK          |          |

| 邀请报告                  | Page 29  |

|                       |          |

| POSTER SESSION        |          |

| 学生海报展示                | Page 128 |

| NATRAO                |          |

| MEMO                  | Dama 463 |

| 附录                    | Page 163 |

**WORKSHOP ON IC ADVANCES IN CHINA**

### **ORGANIZERS & SPONSORS**

### 主办单位与支持单位

#### **ORGANIZED BY**

澳门大学

北京大学

香港科技大学

### **SUPPORTED BY**

河套深港科技创新合作区深圳园区发展署

#### **HOSTED BY**

华芯设集成电路技术中心

#### **DIAMOND SPONSORS**

华为

中兴微电子

知存科技

### **PLATINUM SPONSORS**

兆易创新

纳芯微电子

杰华特微电子

思仪科技

共模半导体

昕原半导体

### **GOLD SPONSORS**

华大九天

纽瑞芯科技

纳瑞科技

#### **MEDIA SUPPORT**

半导体行业观察

IIII

矽说

芯思想

### **CONFERENCE COMMITTEE**

会议组委会

### **CONFERENCE CO-CHAIRS**

路 延,清华大学

Yan Lu, Tsinghua University

陈迟晓,复旦大学

Chixiao Chen, Fudan University

李 强,电子科技大学

Qiang Li, University of Electronic Science and Technology of China

### **TECHNICAL PROGRAM CO-CHAIRS**

孙 楠,清华大学

Nan Sun, Tsinghua University

麦沛然,澳门大学

Pui-In Mak, University of Macau

徐佳伟,复旦大学

Jiawei Xu, Fudan University

刘勇攀,清华大学

Yongpan Liu, Tsinghua University

赵涤燹,东南大学

Dixian Zhao, Southeast University

沈林晓,北京大学

Linxiao Shen, Peking University

张奕涵,香港科技大学

Yihan Zhang, The Hong Kong University of Science and Technology

贾海昆,清华大学

Haikun Jia, Tsinghua University

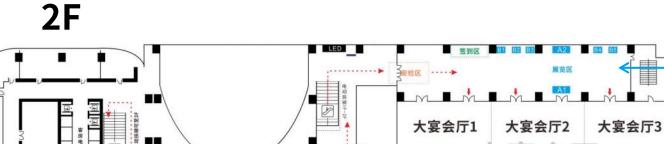

# **CONFERENCE VENUE**

会议地点

### 中国深圳福田香格里拉大酒店

地址: 广东省深圳市福田区中心城益田路 4088 号

知存科技

共模半导体

思仪科技

纳芯微电子

昕原半导体

3F 香格里拉宴会厅 (企业宣讲&欢迎冷餐会) 客房电梯

# **PROGRAM AT A GLANCE**

# 会议日程概览

|             | 2025 年 3 月 25 日 ・ 第 0 天 |        |

|-------------|-------------------------|--------|

| 10:00-20:00 | 会议签到及会议资料领取             | 大宴会厅序厅 |

|             |                         | (2F)   |

|             | 2025 年 3 月 26 日 ・ 第 1 天                                                                         |                 |

|-------------|-------------------------------------------------------------------------------------------------|-----------------|

| 08:30-10:10 | 培训班 1: Design Your Low Power Delta-Sigma ADC: From 0 to 1 谭志超,浙江大学                              | 大宴会厅 1(2F)      |

| 08:30-10:10 | 培训班 2:mm-Wave Oscillator Design<br>殷俊,澳门大学                                                      | 大宴会厅 3(2F)      |

| 10:30-12:10 | 培训班 3:2.5D/3D/3.5D Integration: Fabrication and Chiplet Partition 陈迟晓,复旦大学                      | 大宴会厅 1(2F)      |

| 10:30-12:10 | 培训班 4: High-Performance PLLs: Evolution, Challenges,<br>and Future Directions<br>邓伟,清华大学        | 大宴会厅 3(2F)      |

| 12:10-14:15 | 午 休                                                                                             |                 |

| 14:15-14:30 | ICAC 2025 开幕仪式 &ICAC 2024 最佳报告颁奖                                                                |                 |

| 14:30-15:10 | 大会报告: Trends in the Power Semiconductor Technology 张波,电子科技大学                                    |                 |

| 15:10-15:50 | 大会报告: Recent Progress of Silicon based mm-wave and THz Integrated Circuits and Systems 马凯学,天津大学 | 大宴会厅<br>(2F)    |

| 15:50-16:30 | 大会报告: Computing-in-Memory Processor in the Large-scale AI  Model Era  尹首一,清华大学                  |                 |

| 16:45-18:30 | 企业宣讲 & 欢迎冷餐会                                                                                    | 香格里拉宴会厅<br>(3F) |

| 18:30-21:00 | 学生海报展示                                                                                          | 大宴会厅 1(2F)      |

| 2025 年 3 月 27 日 ・ 第 2 天 |                                                           |                                                  |                                                          |

|-------------------------|-----------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------|

|                         | 大宴会厅 1                                                    | 大宴会厅 2                                           | 大宴会厅 3                                                   |

|                         | Wireless Components<br>and Transcievers<br>主持人:桂小琰        | Integrated Power Circuits<br>主持人:路延              | CIM Techniques I<br>主持人:涂锋斌                              |

| 08:30-08:55             | 麦沛然                                                       | 洪志良                                              | 张锋                                                       |

| 08:55-09:20             | 胡春晓                                                       | 黄沫                                               | 哈亚军                                                      |

| 09:20-09:45             | 赵涤燹                                                       | 屈万园                                              | 陈 勇                                                      |

| 09:45-10:10             | 罗讯                                                        | 童志国                                              | 贾天宇                                                      |

| 10:10-10:30             |                                                           | 茶歇                                               |                                                          |

|                         | High-speed and<br>High-resolution ADCs I<br>主持人:沈林晓       | Amplifiers and Oscillators<br>主持人:潘思宁            | Frequency Synthesizers<br>and RFDACs<br>主持人:秦培           |

| 10:30-10:55             | 孙 楠                                                       | 杨世恒                                              | 张钊                                                       |

| 10:55-11:20             | 陈知行                                                       | 张奕涵                                              | 王 政                                                      |

| 11:20-11:45             | 谭志超                                                       | 胡远奇                                              | 罗登                                                       |

| 11:45-12:10             | 揭 路                                                       | 肖知明                                              | 钱慧珍                                                      |

| 12:10-13:30             | 午 休                                                       |                                                  |                                                          |

|                         | Biomedical Innovations<br>and Advanced Sensors<br>主持人:张奕涵 | Application-Driven<br>Power Management<br>主持人:刘寻 | Digital Circuits for<br>Emerging Applications<br>主持人:于维翰 |

| 13:30-13:55             | 钟龙杰                                                       | 罗文基                                              | 刘勇攀                                                      |

| 13:55-14:20             | 张雅聪                                                       | 郭建平                                              | 刘雷波                                                      |

| 14:20-14:45             | 陈虹                                                        | 刘阳                                               | 焦海龙                                                      |

| 14:45-15:10             | 陈铭易                                                       | 赵广澍                                              | 涂锋斌                                                      |

| 15:10-15:35             | 1                                                         | 路 延                                              | 朱浩哲                                                      |

| 15:35-15:50             |                                                           | 茶 歇                                              |                                                          |

|                         | Wireline Transceivers<br>and Clock Generations<br>主持人:张钊  | High Performance<br>Oscillators<br>主持人:王政        | Analog Circuits for<br>Emerging Applications<br>主持人:张雅聪  |

| 15:50-16:15             | 潘权                                                        | 秦培                                               | 王 成                                                      |

| 16:15-16:40             | 桂小琰                                                       | 吴 亮                                              | 潘思宁                                                      |

| 16:40-17:05             | 郑旭强                                                       | 舒一洋                                              | 鲁文高                                                      |

| 17:05-17:30             | 许灏                                                        | 黄同德                                              | 聂凯明                                                      |

|             | 2025 年 3 月 28 日 ・ 第 3 天                          |                                                          |                                                            |

|-------------|--------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------|

|             | 大宴会厅 1                                           | 大宴会厅 2                                                   | 大宴会厅 3                                                     |

|             | Millimeter-Wave<br>Phased Arrays<br>主持人:郭开喆      | Smart Sensor Interfaces<br>主持人:姜俊敏                       | High Performance<br>Wireless Transceivers<br>主持人:周杰        |

| 08:30-08:55 | 余益明                                              | 罗宇轩                                                      | 宋飞                                                         |

| 08:55-09:20 | 贾海昆                                              | 唐中                                                       | 阳至瞻                                                        |

| 09:20-09:45 | 杨孟儒                                              | 李家明                                                      | 王科平                                                        |

| 09:45-10:10 | 王 カ                                              | 张沕琳                                                      | 李巍                                                         |

| 10:10-10:30 |                                                  | 茶 歇                                                      |                                                            |

|             | Efficient Circuits<br>and Systems<br>主持人:司鑫      | Emerging DC-DC<br>Converters<br>主持人: 邱浩                  | Mixed-Signal Circuits<br>主持人: 王科平                          |

| 10:30-10:55 | 单伟伟                                              | 程林                                                       | 祁 楠                                                        |

| 10:55-11:20 | 王扬                                               | 陈之原                                                      | 赵潇腾                                                        |

| 11:20-11:45 | 杨 杰                                              | 姜俊敏                                                      | 王辉                                                         |

| 11:45-12:10 | 赵 健                                              | 黄俊威                                                      | 陈卓俊                                                        |

| 12:10-13:30 | 午 休                                              |                                                          |                                                            |

|             | CIM Techniques II<br>主持人:陈迟晓                     | Wireless Power Transfer<br>主持人:程林                        | High-speed and<br>High-resolution ADCs II<br>主持人:唐中        |

| 13:30-13:55 | 王源                                               | 邱浩                                                       | 刘佳欣                                                        |

| 13:55-14:20 | 司鑫                                               | 薛仲明                                                      | 沈林晓                                                        |

| 14:20-14:45 | 于维翰                                              | 姚 远                                                      | 沈易                                                         |

| 14:45-15:10 | 薛晓勇                                              | 潘东方                                                      | 潘江鵬                                                        |

| 15:10-15:25 |                                                  | 茶 歇                                                      |                                                            |

|             | Circuits and Systems<br>Beyond 100GHz<br>主持人:余益明 | Wireless Connectivity and<br>Energy Harvester<br>主持人:潘东方 | Wireless Transmitters<br>and mm-Wave Amplifiers<br>主持人:杨孟儒 |

| 15:25-15:50 | 邓 伟                                              | 卢旭阳                                                      | 周杰                                                         |

| 15:50-16:15 | 刘力源                                              | 陈秋锦                                                      | 丰光银                                                        |

| 16:15-16:40 | 陈喆                                               | 张兆博                                                      | 高 立                                                        |

| 16:40-17:05 | 郭开喆                                              | 1                                                        | 杨秉正                                                        |

| 17:05-17:30 | /                                                | ICAC 2025 闭幕仪式 &<br>ICAC 2025 最佳学生海报颁奖                   | /                                                          |

**WORKSHOP ON IC ADVANCES IN CHINA**

# **CONFERENCE SCHEDULE**

会议日程详情

2025年3月25日 · 第0天

| 大宴会厅序厅 | 大宴 | 会厅 | 序厅 |

|--------|----|----|----|

|--------|----|----|----|

### 2025年3月26日 · 第1天

|             |                                                                               | 大宴会厅 1   |

|-------------|-------------------------------------------------------------------------------|----------|

| 08:30-10:10 | 培训班 1: Design Your Low Power Delta-Sigma ADC: From 0 to 1 谭志超,浙江大学            |          |

|             |                                                                               | 大宴会厅 3   |

| 08:30-10:10 | 培训班 2:mm-Wave Oscillator Design<br>殷俊,澳门大学                                    |          |

|             |                                                                               | 大宴会厅 1   |

| 10:30-12:10 | 培训班 3:2.5D/3D/3.5D Integration: Fabrication and Chiplet Partition<br>陈迟晓,复旦大学 |          |

|             |                                                                               | 大宴会厅 3   |

| 10:30-12:10 | 培训班 4: High-Performance PLLs: Evolution, Challenges, and Future Di<br>邓伟,清华大学 | rections |

|             |                                                                               |          |

12:10-14:15 | 午休

### **WORKSHOP ON IC ADVANCES IN CHINA**

### 大宴会厅

| 14:15-14:30 | ICAC 2025 开幕仪式 & ICAC 2024 最佳报告颁奖                                                               |

|-------------|-------------------------------------------------------------------------------------------------|

| 14:30-15:10 | 大会报告: Trends in the Power Semiconductor Technology<br>张波,电子科技大学                                 |

| 15:10-15:50 | 大会报告: Recent Progress of Silicon based mm-wave and THz Integrated Circuits and Systems 马凯学,天津大学 |

| 15:50-16:30 | 大会报告: Computing-in-Memory Processor in the Large-scale AI Model Era<br>尹首一,清华大学                 |

|             | 香格里拉宴会厅 (3F)                                                                                    |

| 16:45-18:30 | 企业宣讲 & 欢迎冷餐会                                                                                    |

|--|

### 2025年3月27日 · 第2天

### 大宴会厅 1

|            | Wireless Components and Transcievers                                         |

|------------|------------------------------------------------------------------------------|

|            | 主持人: 桂小琰                                                                     |

| 08:30      | A BW-Extended Fourth-Order Gain-Boosted N-Path Filter Employing a Switched   |

| Talk #2.1  | gm-C Network                                                                 |

| 1 alk #2.1 | 麦沛然,澳门大学                                                                     |

| 08:55      | A Wideband Replicas-Rejection Digital Transmitter Using Joint-Digital-Analog |

| Talk #2.2  | Interpolation and Filtering in 28nm CMOS                                     |

| 1 dIK #2.2 | 胡春晓,复旦大学                                                                     |

|            | A Packaged 54-to-69-GHz Wideband 2T2R FMCW Radar Transceiver Employing       |

| 09:20      | Cascaded-PLL Topology and PTAT-Enhanced Temperature Compensation in 40-nm    |

| Talk #2.3  | CMOS                                                                         |

|            | 赵涤燹,东南大学                                                                     |

| 09:45      | RFIC: Amplifiers and Array-System                                            |

| Talk #2.4  | 罗讯,电子科技大学                                                                    |

|                    | Integrated Power Circuits                                                   |

|--------------------|-----------------------------------------------------------------------------|

|                    | 主持人: 路延                                                                     |

| 08:30              | Energy Efficiency is the key in PMU and PA design                           |

| Talk #3.1          | 洪志良,复旦大学                                                                    |

| 08:55              | Multi-phase Hybrid DC-DC Converters                                         |

| Talk #3.2          | 黄沫,澳门大学                                                                     |

| 09:20              | A 12A 89.3% Peak Efficiency and 26mV Undershoot 12V/1V Two-Stage Converter  |

| 09.20<br>Talk #3.3 | with Regulated Resonant Switched-Capacitor Regulators                       |

| 1 alk #3.3         | 屈万园,浙江大学                                                                    |

| 09:45              | HOOP: An Auto-Current-Balanced and Easy-Scalable Hybrid Converters Ring for |

| 09.43<br>Talk #3.4 | High Performance Computing                                                  |

| 1 alk #3.4         | 童志国,澳门大学                                                                    |

# 大宴会厅 3

| CIM Techniques I<br>主持人:涂锋斌 |                                                                                                                                                                                      |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08:30 <b>Talk #4.1</b>      | A 28nm 192.3TFLOPS/W Accurate/Approximate Dual-Mode-Transpose Digital 6T-SRAM CIM Macro for Floating-Point Edge Training and Inference 张锋,中国科学院微电子研究所                                |

| 08:55<br><b>Talk #4.2</b>   | eCIMC: A 603.1-TOPS/W eDRAM-Based Cryogenic In-Memory Computing Accelerator Supporting Boolean/Convolutional Operations 哈亚军,上海科技大学                                                   |

| 09:20<br><b>Talk #4.3</b>   | A 28-nm 19.9-to-258.5-TOPS/W 8b Digital Computing-in-Memory Processor With Two-Cycle Macro Featuring Winograd-Domain Convolution and Macro-Level Parallel Dual-Side Sparsity 陈勇,清华大学 |

| 09:45<br><b>Talk #4.4</b>   | Hardware Accelerators for Diffusion Models Leveraging SRAM Compute-in-Memory and Architecture Optimizations 贾天宇,北京大学                                                                 |

10:10-10:30 | 茶 歇

| High-speed and High-resolution ADCs I<br>主持人:沈林晓 |                                                                       |

|--------------------------------------------------|-----------------------------------------------------------------------|

| 10:30                                            | High-Speed Pipelined ADC                                              |

| <b>Talk #5.1</b>                                 | 孙楠,清华大学                                                               |

| 10:55                                            | Diverge from The Origins: ADC and Us?                                 |

| <b>Talk #5.2</b>                                 | 陈知行,澳门大学                                                              |

| 11:20                                            | Energy-Efficient Incremental Delta-Sigma ADCs                         |

| <b>Talk #5.3</b>                                 | 谭志超,浙江大学                                                              |

| 11:45                                            | Filter-Embedded PipeSAR ADC and Floating Charge-Transfering Amplifier |

| <b>Talk #5.4</b>                                 | 揭路,清华大学                                                               |

**WORKSHOP ON IC ADVANCES IN CHINA**

# 大宴会厅 2

| Amplifiers and Oscillators |                                                                                                                                                          |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                            | 主持人:潘思宁                                                                                                                                                  |  |

| 10:30 <b>Talk #6.1</b>     | A 0.4µW/MHz Reference-Replication-Based RC Oscillator with Path-Delay and Comparator-Offset Cancellation Achieving 9.83ppm/℃ from -40 to 125℃ 杨世恒,电子科技大学 |  |

| 10:55<br><b>Talk #6.2</b>  | A 0.36nW, 820 <sub>µ</sub> m2, 32kHz Conduction-Angle-Adaptive Crystal Oscillator in 28nm CMOS for Real-Time Clock Applications<br>张奕涵,香港科技大学            |  |

| 11:20<br><b>Talk #6.3</b>  | A 2.30 NEF Split-Steering Amplifier for Switched-Capacitor Circuits With-14.2-dB CM-CM Gain and 100-V/μs Slew Rate 胡远奇,北京航空航天大学                          |  |

| 11:45<br><b>Talk #6.4</b>  | A 64-Channel Inverter-Based Neural Signal Recording Amplifier With a Novel Differential-Like OTA Achieving an NEF of 0.84 肖知明,南开大学                       |  |

### 大宴会厅 3

| Frequency Synthesizers and RFDACs |                                                                          |  |

|-----------------------------------|--------------------------------------------------------------------------|--|

|                                   | 主持人:秦培                                                                   |  |

| 10:30                             | Design of low-voltage low-jitter PLL: From Integer-N to Fractional-N     |  |

| Talk #7.1                         | 张钊,中国科学院半导体研究所                                                           |  |

| 10:55                             | Low Phase Noise Low Fractional-N Spur Frequency Synthesizer Techniques   |  |

| Talk #7.2                         | 王政,电子科技大学                                                                |  |

| 11:20                             | Design of an All-Digital Fractional Output Divider Using Split-DTC-Based |  |

| Talk #7.3                         | Background Calibration                                                   |  |

| 1 alk #1.5                        | 罗登,国防科技大学                                                                |  |

| 11:45                             | Linearization Techniques for RFDACs                                      |  |

| Talk #7.4                         | 钱慧珍,西安电子科技大学                                                             |  |

12:10-13:30 | 午休

### 大宴会厅 1

|                           | Biomedical Innovations and Advanced Sensors<br>主持人:张奕涵                                                                                                       |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:30 <b>Talk #8.1</b>    | A 3-Axis MEMS Gyroscope with 2.8ms Wake-Up Time Enabled by a 1.5μW Always-On Drive Loop 钟龙杰,西安电子科技大学                                                         |

| 13:55<br><b>Talk #8.2</b> | A High-Voltage-Compliant 86% Peak Efficiency Current-Mode Stimulator With Dynamic Voltage Supply for Implantable Medical Devices 张雅聪,北京大学                    |

| 14:20<br><b>Talk #8.3</b> | ANP-O: A 67µW/Channel, 0.13nW/Synapse/Bit Nose-on-a-Chip for Non-invasive Diagnosis of Diseases with On-chip Incremental Learning 陈虹,清华大学                    |

| 14:45<br><b>Talk #8.4</b> | A 26-G Input-Impedance 112-dB Dynamic-Range Two-Step Direct-Conversion Front-End With Improved 1-Modulation for Wearable Biopotential Acquisition 陈铭易,上海交通大学 |

### 大宴会厅 2

| Application-Driven Power Management<br>主持人:刘寻 |                                                                                                                                                                                                 |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:30<br><b>Talk #9.1</b>                     | A 91.25% Peak Power-Conversion-Efficiency Capacitive Power Management IC Supporting up to 5.68mJ Burst Energy Delivery Using a Single External Capacitor for mm-Scale IoT Applications 罗文基,澳门大学 |

| 13:55<br><b>Talk #9.2</b>                     | Design of DC-DC regulators with Low Quiescent Current and High Power Efficiency for Battery Powered IoT Devices 郭建平,中山大学                                                                        |

| 14:20<br><b>Talk #9.3</b>                     | Pseudo Hysteretic Controlled Gap Time Modulated Isolated DC-DC Converter With Common-Mode Transient Immunity 刘阳,西安电子科技大学                                                                        |

| 14:45<br><b>Talk #9.4</b>                     | High-Efficiency Ultrasound Energy Harvesting Interface with Auto-Calibrated Timing Control from -25 °C to 85 °C 赵广澍,澳门大学                                                                        |

| 15:10<br><b>Talk #9.5</b>                     | A Bi-Directional Dual-Path Boost-48V-Buck Hybrid Converter for HV Power Transmission in Light-Weight Humanoid Robots 路延,清华大学                                                                    |

| Digital Circuits for Emerging Applications<br>主持人:于维翰 |                                                                                                                                                                                                |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:30<br><b>Talk #10.1</b>                            | 3DGS 生成式感知芯片关键技术<br>刘勇攀,清华大学                                                                                                                                                                   |

| 13:55<br><b>Talk #10.2</b>                            | A 28nm 4.05 <sub>µ</sub> J/Encryption 8.72kHMul/s Reconfigurable Multi-Scheme Fully Homomorphic Encryption Processor for Encrypted Client-Server Computing 刘雷波,清华大学                            |

| 14:20<br><b>Talk #10.3</b>                            | Nebula: A 28nm 109.8TOPS/W 3D PNN Accelerator Featuring Adaptive Partition, Multi-Skipping, and Block-Wise Aggregation 焦海龙,北京大学深圳研究生院                                                          |

| 14:45<br><b>Talk #10.4</b>                            | A 28nm 0.22 <sub>µ</sub> J/Token Memory-Compute-Intensity-Aware CNN-Transformer Accelerator with Hybrid-Attention-Based Layer-Fusion and Cascaded Pruning for Semantic-Segmentation 涂锋斌,香港科技大学 |

| 15:10<br><b>Talk #10.5</b>                            | SLAM-CIM: A Visual SLAM Backend Processor With  Dynamic-Range-Driven-Skipping Linear-Solving FP-CIM Macros  朱浩哲,复旦大学                                                                           |

15:35-15:50 | 茶 歇

| Wireline Transceivers and Clock Generations<br>主持人:张钊 |                                                                                                                                                                                       |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:50                                                 | High-Speed SerDes and Optical Communications: Equalizations and Modulations                                                                                                           |

| <b>Talk #11.1</b>                                     | 潘权,南方科技大学                                                                                                                                                                             |

| 16:15                                                 | A Low-Latency 200Gb/s PAM-4 Heterogeneous Transceiver for Retimed Pluggable Optics                                                                                                    |

| <b>Talk #11.2</b>                                     | 桂小琰,西安交通大学                                                                                                                                                                            |

| 16:40<br><b>Talk #11.3</b>                            | A Low-Jitter and Low-Reference-Spur Ring-VCO-Based Injection-Locked Clock Multiplier Utilizing a Complementary-Injection Scheme and an Adaptive Pulsewidth Adjustment 郑旭强,中国科学院微电子研究所 |

| 17:05                                                 | An 8-to-28GHz 8-Phase Clock Generator Using Dual-Feedback Ring Oscillator in 28nm CMOS                                                                                                |

| <b>Talk #11.4</b>                                     | 许灏,复旦大学                                                                                                                                                                               |

# 大宴会厅 2

| High Performance Oscillators |                                                                              |

|------------------------------|------------------------------------------------------------------------------|

| 主持人: 王政                      |                                                                              |

| 15:50                        | A Differential Series-Resonance CMOS VCO with Pole-Convergence Technique     |

| Talk #12.1                   | Achieving 202.1dBc/Hz FoMTA at 10MHz Offset                                  |

| 1 alk # 12.1                 | 秦培,华南理工大学                                                                    |

| 16:15                        | A 47.3-to-58.4GHz Differential Quasi-Class-E Colpitts Oscillator Achieving   |

|                              | 198.8dBc/Hz FoMT                                                             |

| Talk #12.2                   | 吴亮,香港中文大学(深圳)                                                                |

| 16:40                        | Class-G Impedance-Modulation Multi-Core Power Oscillator for High Pout and   |

|                              | Power Back-Off Efficiency Enhancement                                        |

| Talk #12.3                   | 舒一洋,电子科技大学                                                                   |

|                              | An 18.5-to-23.6GHz Quad-Core Class-F23 Oscillator Without 2nd/3rd Harmonic   |

| 17:05                        | Tuning Achieving 193dBc/Hz Peak FoM and 140-to-250kHz 1/f3 PN Corner in 65nm |

| Talk #12.4                   | CMOS                                                                         |

|                              | 黄同德,南京理工大学                                                                   |

|                            | Analog Circuits for Emerging Applications                                                                                                  |  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                            | 主持人:张雅聪                                                                                                                                    |  |  |

| 15:50<br><b>Talk #13.1</b> | Shushan: Cryogenic Silicon Integrated Circuits for the High Fidelity Quantum Interface 王成,电子科技大学                                           |  |  |

| 16:15<br><b>Talk #13.2</b> | A 143dB Dynamic Range 119dB CMRR Capacitance-to-Digital Converter for High-Resolution Floating-Target Displacement Sensing 潘思宁,清华大学        |  |  |

| 16:40<br><b>Talk #13.3</b> | A 320×256 6.9mW 2.2mK-NETD 120.4dB-DR LW-IRFPA with Pixel-Paralleled Light-Driven 20b Current-to-Phase ADC 鲁文高,北京大学                        |  |  |

| 17:05<br><b>Talk #13.4</b> | A 1920 $\times$ 1080 Array 2D/3D Image Sensor with 3 $\mu$ s Row-Time Single-Slope ADC and 100MHz Demodulated PPD locked-in Pixel 聂凯明,天津大学 |  |  |

### 2025年3月28日 · 第3天

### 大宴会厅 1

| Millimeter-Wave Phased Arrays<br>主持人:郭开喆 |                                                                                                                                                            |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08:30 <b>Talk #14.1</b>                  | A Reconfigurable Phased-Array Transceiver Front-End for 5G New Radio<br>余益明,电子科技大学                                                                         |

| 08:55 <b>Talk #14.2</b>                  | Research on Millimeter-wave Multi-beam Phased Array in CMOS Process<br>贾海昆,清华大学                                                                            |

| 09:20 <b>Talk #14.3</b>                  | K/Ka-Band Hybrid-Packaged Four-Element Four-Beam Phased-Array Transmitter and Receiver Front-Ends With Optimized Beamforming Passive Networks 杨孟儒,南京航空航天大学 |

| 09:45 <b>Talk #14.4</b>                  | A Compact Ka-Band Phased-Array Transmitter with On-Chip Phase-Locked Loop<br>王力,香港科技大学                                                                     |

| Smart Sensor Interfaces<br>主持人:姜俊敏 |                                                                                                                                                                                                                                  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08:30<br><b>Talk #15.1</b>         | Sensor Interface Circuits for Large-Scale Tactile Sensing<br>罗宇轩,浙江大学                                                                                                                                                            |

| 08:55<br><b>Talk #15.2</b>         | A Sub-1V 14b BW/Power Scalable CT Sensor Interface with a Frequency-Controlled Current Source 唐中,杭州万高科技股份有限公司                                                                                                                    |

| 09:20<br><b>Talk #15.3</b>         | A 4,100 $\mu$ m2 Wire-Metal-Based Temperature Sensor with a Fractional-Discharge FLL and a Time-Domain Amplifier with $\pm 0.2$ °C Inaccuracy (3 $\sigma$ ) from $-40$ to 125°C and 45fJ·K2 Resolution FoM in 28nm CMOS 李家明,澳门大学 |

| 09:45 <b>Talk #15.4</b>            | Millimeter-sized Wireless Electrochemical Sensing SoC<br>张沕琳,清华大学                                                                                                                                                                |

# 大宴会厅 3

| High Performance Wireless Transceivers |                                                                                 |  |

|----------------------------------------|---------------------------------------------------------------------------------|--|

|                                        |                                                                                 |  |

| 08:30                                  | A 28nm Multimode Multiband RF Transceiver with Harmonic Rejection TX and Spur   |  |

| Talk #16.1                             | Avoidance RX Supporting LTE Cat1bis                                             |  |

| 1 alk # 16.1                           | 宋飞,芯翼信息科技(上海)有限公司                                                               |  |

| 08:55                                  | Power-efficient Transceiver Techniques for Long-Range IoT Applications          |  |

| Talk #16.2                             | 阳至瞻,澳门大学                                                                        |  |

| 09:20                                  | A Low-Power Blocker-Tolerant Wideband Receiver With Bias-Tunable Mixer and      |  |

| 09:20<br>Talk #16.3                    | Effective Switch Resistance Compensation                                        |  |

|                                        | 王科平,天津大学                                                                        |  |

|                                        | Compact Full-Duplex Receiver with Wideband Multi-Domain                         |  |

| 09:45                                  | Hilbert-Transform-Equalization Cancellation Based on Multi-Stage APFs Achieving |  |

| Talk #16.4                             | 65dB SIC Across 120MHz BW                                                       |  |

|                                        | 李巍,复旦大学                                                                         |  |

10:10-10:30 | 茶 歇

|                            | Efficient Circuits and Systems                                                                                                                   |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | 主持人: 司鑫                                                                                                                                          |

| 10:30 Talk #17.1           | DSC-TRCP: Dynamically Self-Calibrating Tunable Replica Critical Paths Based Timing Monitoring for Variation Resilient Circuits                   |

|                            | 单伟伟,东南大学                                                                                                                                         |

| 10:55 <b>Talk #17.2</b>    | A Versatile Transformer Accelerator With Low-Rank Estimation and Heterogeneous Dataflow 王扬,清华大学                                                  |

| 11:20<br><b>Talk #17.3</b> | An Energy-Efficient Unstructured Sparsity-Aware Deep SNN Accelerator With 3-D Computation Array 杨杰,西湖大学                                          |

| 11:45 <b>Talk #17.4</b>    | A 0.67-to-5.4 TSOPs/W Spiking Neural Network Accelerator With 128/256 Reconfigurable Neurons and Asynchronous Fully Connected Synapses 赵健,上海交通大学 |

# 大宴会厅 2

|                            | Emerging DC-DC Converters                                                        |  |

|----------------------------|----------------------------------------------------------------------------------|--|

|                            | 主持人: 邱浩                                                                          |  |

| 10:30                      | A Multi-Core Isolated DC-DC Converter with Embedded Magnetic-Core Transformer    |  |

| Talk #18.1                 | and Low EMI Emissions                                                            |  |

| 1 aik # 18.1               | 程林,中国科学技术大学                                                                      |  |

|                            | Enhancing Efficiency in Piezoelectric Energy Harvesting: Cross-Flip Synchronized |  |

| 10:55                      | Switch Harvesting on Capacitors Rectifier and Multi-Output DC-DC Converters      |  |

| Talk #18.2                 | Utilizing Shared Capacitors                                                      |  |

|                            | 陈之原,复旦大学                                                                         |  |

| 11:20                      | Batter-to-36V Continous Current Boost Converter                                  |  |

| Talk #18.3                 | 姜俊敏,南方科技大学                                                                       |  |

| 11:45<br><b>Talk #18.4</b> | A Dual-Loop Non-Uniform-Multi-Inductor Hybrid DC-DC Converter with Specified     |  |

|                            | Inductor Current Allocation and Fast Transient Response                          |  |

|                            | 黄俊威,澳门大学                                                                         |  |

### 大宴会厅 3

|                            | Mixed-Signal Circuits                                                                                                                                      |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 主持人:王科平                    |                                                                                                                                                            |  |

| 10:30                      | Silicon-Photonic Transceiver Design for Co-Packaged Optics                                                                                                 |  |

| Talk #19.1                 | 祁楠,中国科学院半导体研究所                                                                                                                                             |  |

| 10:55                      | A Reference-Less CDR Using SAR-Based Frequency Acquisition Technique Achieving 55ns Constant Band-Searching Time and up to 63.64 Gb/s/µs Acquisition Speed |  |

| Talk #19.2                 | 赵潇腾,西安电子科技大学                                                                                                                                               |  |

|                            | A 1.8GHz-3.0GHz Fully Integrated All-In-One CMOS Frequency Management                                                                                      |  |

| 11:20                      | Module Achieving -47/+42ppm Inaccuracy from -40°C to 95°C and -150/+70ppm                                                                                  |  |

| Talk #19.3                 | After Accelerated Aging                                                                                                                                    |  |

|                            | 王辉,上海交通大学                                                                                                                                                  |  |

| 11:45<br><b>Talk #19.4</b> | A Compute-in-Memory Annealing Processor with Interaction Coefficient Reuse and                                                                             |  |

|                            | Sparse Energy Computation for Solving Combinatorial Optimization Problems                                                                                  |  |

|                            | 陈卓俊,湖南大学                                                                                                                                                   |  |

12:10-13:30 | 午休

# 大宴会厅 1

|                     | CIM Techniques II                                                               |  |

|---------------------|---------------------------------------------------------------------------------|--|

|                     | 主持人: 陈迟晓                                                                        |  |

| 13:30               | SKADI: A 28nm Complete K-SAT Solver Featuring Dual-Path SRAM-Based Macro        |  |

| Talk #20.1          | and Incremental Update with 100% Solvability                                    |  |

| 1 alk #20. 1        | 王源,北京大学                                                                         |  |

|                     | A 28nm 17.83-62.84TFLOPS/W Broadcast-Alignment                                  |  |

| 13:55               | Floating-Point-Compute-in-Memory Macro with Non-2's Complement MAC for          |  |

| Talk #20.2          | CNNs and Transformers                                                           |  |

|                     | 司鑫,东南大学                                                                         |  |

| 14:20               | Breaking the Readout Wall: Energy Efficient In-Memory Processing Techniques for |  |

| 14.20<br>Talk #20.3 | AIoT                                                                            |  |

| 1 alk #20.3         | 于维翰,澳门大学                                                                        |  |

| 14:45               | High-Density SRAM Design for Computing in Memory                                |  |

| Talk #20.4          | 薛晓勇,复旦大学                                                                        |  |

|                            | Wireless Power Transfer                                                       |  |

|----------------------------|-------------------------------------------------------------------------------|--|

|                            | 主持人:程林                                                                        |  |

| 13:30                      | A 6.78-MHz Single-Stage Regulating Rectifier with Dual Outputs Simultaneously |  |

| Talk #21.1                 | Charged in a Half Cycle Achieving 92.2%-Efficiency and 131-mW Output Power    |  |

|                            | 邱浩,南京大学                                                                       |  |

|                            | A 6.78MHz 94.2% Peak Efficiency Class-E Transmitter with Adaptive Real-part   |  |

| 13:55                      | Impedance Matching and Imaginary-part Phase Compensation Achieving a 33W      |  |

| Talk #21.2                 | Wireless Power Transfer System.                                               |  |

|                            | 薛仲明,西安交通大学                                                                    |  |

| 14:20                      | A 13.56-MHz Single-Input Dual-Output Wireless Power and Data Transfer System  |  |

| Talk #21.3                 | for Bio-Implants                                                              |  |

|                            | 姚远,香港科技大学                                                                     |  |

| 14:45<br><b>Talk #21.4</b> | A Dual-LC-Resonant Isolated DC-DC Converter Achieving 65.4% Peak Efficiency   |  |

|                            | and Inherent Backscattering                                                   |  |

|                            | 潘东方,中国科学技术大学                                                                  |  |

# 大宴会厅 3

| High-speed and High-resolution ADCs II |                                                                                     |

|----------------------------------------|-------------------------------------------------------------------------------------|

|                                        | 主持人: 唐中                                                                             |

| 13:30                                  | A Fully Dynamic Noise-Shaping SAR ADC Achieving 120dB SNDR and 189dB FoMs           |

| Talk #22.1                             | in 1kHz BW                                                                          |

|                                        | 刘佳欣,电子科技大学                                                                          |

| 13:55                                  | Rail-to-Rail ADC Input Buffer Designs Employing Continuous-Time Correlated Level    |

| 15.55<br>Talk #22.2                    | Shifting and Split Coarse-Fine Techniques                                           |

| 1 dIK #22.2                            | 沈林晓,北京大学                                                                            |

| 14:20                                  | <b>Energy-Efficient Pipelined ADC with Parallel-Operation SAR Sub-Quantizer and</b> |

| Talk #22.3                             | Dynamic Deadzone Ring Amplifier                                                     |

| 1 alk #22.3                            | 沈易,西安电子科技大学                                                                         |

| 14:45                                  | Bandpass Delta-Sigma modulators based on N-path Filters                             |

| Talk #22.4                             | 潘江鵬,香港中文大学                                                                          |

15:10-15:25 | 茶 歇

|            | Circuits and Systems Beyond 100GHz                                    |  |

|------------|-----------------------------------------------------------------------|--|

|            | 主持人: 余益明                                                              |  |

| 15:25      | D-Band Distributed MIMO Radar Transceiver and System                  |  |

| Talk #23.1 | 邓伟,清华大学                                                               |  |

| 15:50      | A 3 THz CMOS Image Sensor                                             |  |

| Talk #23.2 | 刘力源,中国科学院半导体研究所                                                       |  |

| 16:15      | Silicon-based THz Direct Modulation Communications                    |  |

| Talk #23.3 | 陈喆,东南大学                                                               |  |

| 16:40      | A 0.68-THz Receiver With Third-Order Subharmonic Mixing in 65-nm CMOS |  |

| Talk #23.4 | 郭开喆,东南大学                                                              |  |

# 大宴会厅 2

| Wireless Connectivity and Energy Harvesters |                                                                             |

|---------------------------------------------|-----------------------------------------------------------------------------|

| 主持人:潘东方                                     |                                                                             |

| 15:25                                       | Integrated Wireless Power Transfer, Communication, and Actuation            |

| Talk #24.1                                  | 卢旭阳,上海交通大学                                                                  |

| 15:50<br><b>Talk #24.2</b>                  | A Single-Input RF Energy-Harvesting Interface With Compensated-CEPE Control |

|                                             | and 3-D Hill-Climbing MPPT Achieving — 28.5 dBm Sensitivity                 |

|                                             | 陈秋锦,澳门大学                                                                    |

| 16:15<br><b>Talk #24.3</b>                  | A High-Effieiency Low-Cost Multi-Antenna RF Energy Harvesting System With   |

|                                             | Leakage Suppression                                                         |

|                                             | 张兆博,南方科技大学                                                                  |

|                            | Wireless Transmitters and mm-Wave Amplifiers                                   |

|----------------------------|--------------------------------------------------------------------------------|

|                            | 主持人: 杨孟儒                                                                       |

| 15:25<br><b>Talk #25.1</b> | A Phase-Modulation Phase-Shifting Phased-Array Transmitter With Phase          |

|                            | Self-Calibration and Deep PBOs Efficiency Enhancement                          |

|                            | 周杰,电子科技大学                                                                      |

| 15.50                      | Silicon-Based Wideband Low-Noise Amplifier for mm-Wave Wireless                |

| 15:50 <b>Talk #25.2</b>    | Communications                                                                 |

|                            | 丰光银,华南理工大学                                                                     |

| 16.15                      | A Compact Millimeter-wave Reconfigurable Dual-band LNA with Image-rejection in |

| 16:15                      | 28-nm Bulk CMOS for 5G Application                                             |

| Talk #25.3                 | 高立,华南理工大学                                                                      |

|                            | A 56-to-64GHz Linear Power Amplifier with 30.2dBm Psat and 23.5% PAEpeak Using |

| 16:40                      | Scalable Matched-Zone-Expanding Radial Power Combining with EM-Loss            |

| Talk #25.4                 | Reduction in 40nm Bulk CMOS                                                    |

|                            | 杨秉正,电子科技大学                                                                     |

|                            | 大宴会厅 2                                                                         |

| 17:05-17:30                | ICAC 2025 闭幕仪式 & ICAC 2025 最佳学生海报颁奖                                            |

**WORKSHOP ON IC ADVANCES IN CHINA**

### **PLENARY TALK**

大会报告

张波

2025 年 3 月 26 日 · 第 1 天 大宴会厅

Talk #1.1 / 14:30-15:10

#### 电子科技大学

张波,电子科技大学集成电路研究中心主任,教授、博导,天府杰出科学家,四川省优秀教师。兼(曾)任国家 01、02 科技重大专项总体组专家,中国电源学会元器件专委会主任,四川电子学会半导体集成技术 专委会主任等。长期从事功率半导体芯片技术研究,以第一完成人两次荣获国家科技进步二等奖(2010 年度、2023 年度),并获国家及省部级科技奖励 18 项,发表 SCI 论文 800 余篇,授权中美发明专利 400 余项,带领电子科技大学功率集成技术实验室已培养毕业 1200 余名研究生,为全球功率半导体领域最大的人 才培养基地;产学研合作成效显著,与企业合作开发工艺与产品 200 余项,为合作企业新增直接经济效益 达数百亿元人民币。

#### **TALK**

#### **Trends in the Power Semiconductor Technology**

The presentation focuses on the trends in the power semiconductor technology. It analyzes the development trend of power semiconductor devices from the fields of "More Silicon" and "More than Silicon", and analyzes the development of silicon-based power semiconductor devices by taking "More MOSFET" and "More IGBT" as examples. The development of power semiconductor devices not only needs to continuously improve the performance of power semiconductor devices based upon the device structure, but also needs to improve the process, larger wafers, thinner wafers, smaller size, more integration, and using of VLSI advanced process is an important direction for the development of power semiconductor devices. The development of power semiconductor devices should merge "More Devices" and "More Than Devices". Different applications have different performance requirements for the same type of device. There is no best device, only the suitable product. In the More Than Silicon section, the presentation provides an analysis of the development trends of the most popular wide-bandgap power semiconductor devices.

**WORKSHOP ON IC ADVANCES IN CHINA**

马凯学

# 2025年3月26日·第1天 大宴会厅

Talk #1.2 / 15:10-15:50

### 天津大学

天津大学讲席教授、博导、IEEE Fellow、中国电子学会会士、国家杰青、国务院特殊津贴专家。现任天津大学微电子学院院长、天津国家"芯火"双创平台负责人、智能传感材料全国重点实验室副主任、天津市集成电路协会会长、天津市成像与感知微电子技术重点实验室主任等。从业 27 年(企业 10 年)先后在航天504 所和新加坡科技电子等单位工作。从事射频、毫米波电路与系统和天线传播研究,国际上提出集成悬置线集成电路和可重构毫米波芯片技术,承担国家重点研发专项和国家重点基金等项目。发表英文专著3部,IEEE 期刊文章240余篇,专利60余项,成果落地应用获天津市科技进步一等奖等奖项,入选天津市杰出人才和"天津发展人才先锋"十大年度人物等。曾任中国电子学会青年科学家微波与电路系统专委会首任主任和国际微波期刊IEEE TMTT 副主编等。担任中国电子学会空间电子学分会副主任委员等。

#### **TALK**

#### Recent Progress of Silicon based mm-wave and THz Integrated Circuits and Systems

With the advantages of excellent penetration, broad bandwidth and good security, millimeter-wave (mm-wave) and Terahertz (THz) has been drawn much attention in China, USA, Europe and worldwide for both academy and industry society. mm-wave band has been already assigned for future 5G/6G applications and THz technique has been recognized as the one of ten techniques in 21 century which can change the future world. With down-scaling of the commercial silicon process, which has been verified as one of excellent candidates for commercial 5G/6G mm-wave and THz applications like communication and sensing etc. in terms of the low cost, compact size and high integrity etc. This talk will present the progress silicon based circuits and systems of mm-wave and THz. The chips development of our group in the frequency range like 28GHz/39GHz, 140GHz, 220GHz, 2.5THz and up to 28.3THz will also be introduced. The challenge and future trend of the silicon-based mm-wave and THz will also be presented.

**WORKSHOP ON IC ADVANCES IN CHINA**

尹首-

# 2025年3月26日·第1天 大宴会厅

Talk #1.3 / 15:50-16:30

### 清华大学

尹首一,清华大学教授,集成电路学院副院长,IEEE Fellow,国家杰出青年科学基金获得者,中国高被引学者。研究方向为可重构计算、人工智能芯片设计。 已发表学术论文 200 余篇,包括 ISSCC、VLSI、ISCA、MICRO、HPCA、DAC 和 IEEE JSSC、TPDS、TCSVT、TVLSI、TCAS-I/II 等集成电路和体系结构领域学术会议和权威期刊。出版《可重构计算》《人工智能芯片设计》专著 2 部。曾获国家技术发明二等奖、中国电子学会技术发明一等奖、中国发明专利金奖、教育部技术发明一等奖、江西省科技进步二等奖、中国电子学会优秀科技工作者奖、中国电子信息领域优秀科技论文奖。现任集成电路领域国际会议 ISCA、MICRO、FPGA 和 A-SSCC 的技术委员会委员,《中国科学:信息科学》编委,国际期刊《ACM Transactions on Reconfigurable Technology and Systems》及《Integration, the VLSI Journal》的 Associate Editor。

#### **TALK**

#### **Computing-in-Memory Processor in the Large-scale AI Model Era**

With the rapid development of large-scale AI models represented by DeepSeek, AI computing has entered a new era. The massive parameter scale and multimodal learning capabilities of large models enable them to handle more complex and general-purpose intelligent tasks, while also raising tremendous demand for high-performance AI processors. However, the frequent and extensive data movement severely restricts the AI processor performance due to the von Neumann bottleneck. Computing-in-memory (CIM) architecture, which deeply integrates compute and memory, offers a promising solution to break through this limitation and achieve a balance between high performance and energy efficiency. However, in the large-scale AI model era, CIM processors face new challenges such as mixed-precision computing, sparsity processing, massive parameter storage, and inter-chip communication. This report will discuss how to design CIM processors with multi-level architecture innovations to tackle these challenges and provide high-performance and efficient support for the large-scale AI model deployment.

**WORKSHOP ON IC ADVANCES IN CHINA**

### **TUTORIAL**

# 芯片设计培训班

2025年3月26日 · 第1天

大宴会厅 1

08:30-10:10

#### 浙江大学

Zhichao Tan (Senior Member, IEEE) received the B.Eng. degree from Xi'an Jiaotong University, Xi'an, China, in 2004, the M.Eng. degree from Peking University, Beijing, China, in 2008, and the Ph.D. degree from Delft University of Technology, Delft, The Netherlands, in 2013.

He was a Staff IC Design Engineer working on low-power, high-precision analog/mixed-signal circuit design with Analog Devices Inc., Wilmington, MA, USA, from 2013 to 2019. He joined Zhejiang University, Hangzhou, China, as a Faculty Member in 2019. His research interests include energy-efficient sensor interfaces, precision analog circuits, and ultra-low-power analog-to-digital converters (ADCs). This has resulted in over 85 technical journal and conference papers. He holds five U.S. patents.

Dr. Tan is a TPC member of the IEEE Custom Integrated Circuits Conference. He was a TPC member of the IEEE Asian Solid-State Circuits Conference. He has served as Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS, IEEE Sensors Journal, and IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS.

#### **TUTORIAL**

#### **Design Your Low Power Delta-Sigma ADC:** From 0 to 1

Delta-Sigma ADCs are the most widely used solutions to high-precision conversion applications. This tutorial provides a comprehensive overview of delta-sigma ADCs with basic principles and design examples. We start with the concepts of oversampling and noise shaping. We cover various behavioral topologies and circuit implementations of delta-sigma ADCs, revealing the trade-offs and design considerations for higher energy efficiency. Recent advances in low-power delta-sigma ADCs will also be provided. This tutorial provides intuitive explanations and design insights, aiming to help the beginners have a solid understanding and quickly get started with designing their own delta-sigma ADCs.

**WORKSHOP ON IC ADVANCES IN CHINA**

殷俊

# 2025年3月26日・第1天

大宴会厅3

08:30-10:10

### 澳门大学

殷俊于 2004 和 2007 年分别获得北京大学微电子学士和硕士学位,并于 2013 年获得香港科技大学电子与计算机工程博士学位。现为澳门大学模拟与混合信号超大规模集成电路国家重点实验室副教授。他的研究方向包括时钟产生与低功耗无线收发机芯片,于本领域高水平国际期刊与会议发表论文超过 90 篇。殷教授现担任国际固态电路会议 ISSCC 以及欧洲固态电路会议 ESSCIRC 的技术委员会成员。他还曾担任电路与系统领域旗舰期刊-电路与系统学报 TCAS-I 的副主编(2020-2023),以及亚洲固态电路会议 A-SSCC 的技术委员会成员(2019, 2021-2022)。

#### **TUTORIAL**

#### mm-Wave Oscillator Design

High-performance, low-phase-noise oscillators are heavily demanded by high-throughput and high-fidelity mm-wave transceivers. The content of this tutorial includes: (1) the oscillator's performance matrix and key Figure of Merit (FoM); (2) the reactive-load design, namely - inductors/transformers and tunable capacitors, for achieving high quality factor and the design challenge for mm-wave oscillators; (3) various oscillator topologies to reduce phase noise at the mm-wave frequency, such as Class-C and harmonic shaping; (4) the design of multi-core synchronized oscillator, which provides an opportunity for further reducing phase noise; (5) frequency tuning range extension for multi-core oscillators with the aid of mode-switching and multi-resonance techniques.

**WORKSHOP ON IC ADVANCES IN CHINA**

陈迟晓

2025年3月26日・第1天 大宴会厅1

10:30-12:10

### 复旦大学

陈迟晓。复旦大学芯片与系统前沿技术研究院副研究员,集成芯片与系统全国重点实验室集成芯片创新中心主任、绍芯实验室(复旦-绍兴研究院)副主任、国家优青、上海市青年科技启明星。主要研究领域包括面向 AI 芯片的跨层次设计方法学、感存算一体电路与架构、Chiplet 异质异构集。以第一、通信作者发表多篇集成电路设计领域的高水平论文,包括 ISSCC、MICRO、HPCA、DAC、IEEE JSSC, TCAS-I/II,JETCAS 等。任亚洲固态电路会议 A-SSCC 技术委员会成员。

#### **TUTORIAL**

#### 2.5D/3D/3.5D Integration: Fabrication and Chiplet Partition

随着人工智能时代大模型、大算力需求的飞速发展,基于传统单芯片高性能处理器的设计方法面临存储墙、功耗墙和面积墙等诸多技术瓶颈。基于精密半导体工艺的 2.5D/3D 集成技术为新一代高性能处理器提供了新的基于。本次培训将介绍 2.5D/3D/3.5D 集成工艺的基本原理,如硅中阶层、硅通孔等。同时,也将介绍高性能计算处理器芯片设计中,在基于上述 2.5D/3D 工艺时,互连接口的电路设计,以及系统架构如何实现分解,并介绍团队在基于有源硅中介层(Active Interposer)的设计要点。

**WORKSHOP ON IC ADVANCES IN CHINA**

邓伟

2025年3月26日・第1天

大宴会厅3

10:30-12:10

### 清华大学

清华大学长聘副教授,入选国家高层次人才计划和国家青年人才计划。电子科技大学学士和硕士,日本东京工业大学博士,曾在美国苹果公司总部任资深主任工程师,负责面向高速无线通信 SoC 的毫米波和混合信号芯片设计。现任职清华大学集成电路学院,主要研究方向为硅基射频/毫米波/太赫兹芯片设计与系统集成。

现任 ISSCC、VLSI、CICC、RFIC、A-SSCC 和 ESSCIRC 的技术委员会成员,IEEE SSCS 杰出讲师,以及 IEEE JSSC、IEEE SSC-L、半导体学报等期刊副主编或客座编辑,负责射频和无线方向。在 JSSC、IEEE T-CAS I、IEEE T-MTT 等期刊以及 ISSCC、VLSI 等国际会议发表论文 160 余篇,其中在 JSSC 和 ISSCC 发表论文 40 余篇;主持射频和无线芯片设计领域的多项国家重点科研项目。

#### **TUTORIAL**

#### **High-Performance PLLs: Evolution, Challenges, and Future Directions**

Phase-locked loop (PLL) is one of the key techniques for both communication and radar systems. Various functions in communication and radar systems, including clock generation, frequency synthesis, serial-to-parallel conversion, frequency and phase modulation, clock synchronization and distribution, coherent and non-coherent demodulation, clock and carrier recovery, directly or indirectly rely on PLLs. High performance PLL is one of the cutting-edge topics in the field of integrated circuit and system design. It involves various research directions such as mixed-signal circuit design, digital algorithms, and system-level architecture. This lecture will discuss the high-performance PLL circuit and architecture evolution, review the latest research progress and discuss the future development trends of high-performance PLLs.

### **INVITED TALK**

邀请报告

麦沛然

2025年3月27日・第2天 大宴会厅1

Talk #2.1 / 08:30-08:55

### 澳门大学

麦沛然,澳门大学教授、模拟与混合信号超大规模集成电路国家重点实验室主任、微电子研究院副院长、长江学者讲座教授、澳门教育功绩勋贤、葡国科学院院士(外籍)、中国科学院海外专家、IEEE Fellow、IET Fellow 和英国皇家化学会会士(RSC Fellow)。麦教授先后担任 IEEE SSCS 和 CASS 理事会委员、CASS 杰出演讲人主席、IEEE SSCS 和 CASS 杰出演讲人主席、IEEE SSCS 和 CASS 杰出演讲人。麦教授主要从事集成电路和跨学科系统研究,在模拟和射频电路理论与设计、数字微流控技术与应用、微型核磁共振和成像等领域具有广泛影响力。先后主持国家重点实验室项目、粤港澳聯合實驗室项目、港澳科技成果来粤转化项目、澳门科学技术发展基金重点研发专项和国家科技部联合项目等 10 余项。孵化高科技公司实现了模拟电路和数字微流控技术的产业化。麦教授先后担任 IEEE Solid-State Circuits Letters (SSCL)总主编,IEEE Press、JSSC、TCAS-I、TCAS-II、JETCAS 和 SSCL等高级/副主编,国际会议 ISSCC,ESSCIRC 和 A-SSCC 委员和联合创办华人芯片设计技术研讨会 ICAC。麦教授 2011 年获国家科学技术进步二等奖、2019 年获国庆 70 周年纪念章和选为国庆 70周年彩车人物代表、国庆 75 周年国宴代表、2012 年起获澳门科技发明奖和特别奖共 9 项、2022 年获澳门首个腾讯科学探索奖和 2023 年获 ISSCC 70 周年杰出贡献者奖等。麦教授长期致力于电路设计普及和推广,在世界一流大学和芯片公司作专题讲学 100 余次,并多次于 IEEE 国际会议作主题演讲,在顶级期刊和国际学术会议上发表论文 500 余篇,在 IEEE 核心系列期刊上发表论文 150 余篇(含 JSSC 54 篇),获授权中国及美国发明专利 30 余项。2011 至 2025 年间连续 15 年发表国际顶尖会议 ISSCC 论文共 44 篇。

#### **TALK**

#### A BW-Extended Fourth-Order Gain-Boosted N-Path Filter Employing a Switched gm-C Network

This work is a bandwidth (BW)-extended gain-boosted N-path filter with a switched gm–C network, in which a 4th-order response is achieved with the subtraction method by shifting the baseband (BB) admittance with poly-phase gm cells in the BB. It features not only in-band RF gain and high- Q bandpass response but also other valuable properties, such as a wide passband BW and a high linearity. In addition, a class-A/-B amplifier is employed to provide the RF gain, in which the linearity is optimized with a tunable bias voltage. Fabricated in a 65-nm CMOS process, our proposed filter measures a 10.7–12.7-dB voltage gain and a 5.3–6.2-dB noise figure (NF) over a 0.5–1.5-GHz RF range. With gm-linearity optimization, our filter centered at 1 GHz exhibits an out-of-band input-referred 3rd-order intercept point (OB-IIP3) of 18.2 dBm and a passband BW of 50 MHz. The ultimate stopband rejection of the filter is >50 dB. The power consumption is 11.1–15.9 mW, and the die area is 0.083 mm^2.

**WORKSHOP ON IC ADVANCES IN CHINA**

2025年3月27日・第2天 大宴会厅1

Talk #2.2 / 08:55-09:20

### 复旦大学

Chunxiao Hu received the B.S. degree from the Nanjing University of Posts and Telecommunications, Nanjing, China, in 2017, the M.S. degree from the University of Chinese Academy of Sciences, Beijing, China, in 2020, and the Ph.D. degree with the School of Microelectronics from Fudan University, Shanghai, China, in 2024. Her research interests focus on energy-efficient all-digital transmitters, digitized RF circuits and digital baseband signal processing circuits.

#### **TALK**

# A Wideband Replicas-Rejection Digital Transmitter Using Joint-Digital-Analog Interpolation and Filtering in 28nm CMOS

A wideband replicas-rejection DTX with joint-digital-analog interpolation and filtering technique is proposed. Polyphase architecture with equivalence order of operations is employed for better replicas rejection with low power consumption. Integration of analog interpolation into DPA along with pre-filter further eliminates replicas to support wideband applications. The DTX achieves wide frequency coverage of 2.1-5.1GHz, peak Pout of 27.8dBm with 30.4% SE, >42dBc wideband replicas rejection, and only 0.88mm2 core size with a single 1.1V supply.

**WORKSHOP ON IC ADVANCES IN CHINA**

赵涤燹

# 2025年3月27日・第2天 大宴会厅1

Talk #2.3 / 09:20-09:45

### 东南大学

赵涤燹,东南大学教授,紫金山实验室教授,天锐星通首席科学家。主要研究方向为 5G 毫米波通信和宽带卫星通信 CMOS 毫米波芯片和集成相控阵,发表论文 120 余篇。研究成果入选 2020 年度高等学校十大科技进展,国家十三五科技成果展,2021 年度中国电子学会科学技术奖(技术发明)一等奖,2022 年度中国半导体十大研究进展,2022 年度信息通信领域十大科技进展,2023 年度国家技术发明二等奖。

#### **TALK**

# A Packaged 54-to-69-GHz Wideband 2T2R FMCW Radar Transceiver Employing Cascaded-PLL Topology and PTAT-Enhanced Temperature Compensation in 40-nm CMOS

This talk presents a highly integrated V-band frequency-modulated-continuous-wave (FMCW) radar transceiver (TRX) in 40-nm bulk CMOS. It incorporates two identical transmitter (TX) and receiver (RX) channels, enabling not only traditional forward sensing but also full-360° detection. The FMCW synthesizer is based on a cascaded-phase-locked-loop (PLL) topology, enhancing chirp quality while reducing the necessity for complex off-chip components. A proportional-to-absolute-temperature (PTAT)-enhanced temperature compensation (TC) technique is proposed to improve the temperature robustness at V-band. The impacts of clock synchronization and temperature insensitivity of the TRX on FMCW radar systems are also discussed. For broadband, high-linearity, and low-noise operation within limited stages, RF front-ends are carefully designed with the optimization strategy elaborated. The proposed TRX achieves a 3-dB bandwidth ranging from 54 to 69 GHz. The RX features a 67-dB tuning range of the conversion gain (CG) and a 10-dB noise figure (NF). The Psat of TX is 12.8 dBm. The PTAT-enhanced TC effectively minimizes variations in CG, NF, and PSAT, maintaining less than 2.1-, 2.9-, and 2.5-dB changes, respectively, from -55 °C to 105 °C. The FMCW generator achieves a chirp rate of 468.5 MHz/µs with a bandwidth of 7.2 GHz, demonstrating a minimal 0.019% chirp error.

**WORKSHOP ON IC ADVANCES IN CHINA**

罗证

2025年3月27日・第2天 大宴会厅1

Talk #2.4 / 09:45-10:10

### 电子科技大学

罗讯,博士,电子科技大学教授;国家高层次人才计划入选者、IEEE 杰出青年工程师奖获得者、爱思唯尔斯坦福大学全球前 2%顶尖科学家(终身/年度)。研究方向:射频集成电路及其系统集成、可重构无源电路与模组、微型化三维集成封装等。兼任/曾任 IEEE Microwave and Wireless Components Letters 责任主编、IEEE Journal of Microwaves 领域编辑、IEEE Open Journal of the Solid-State Circuits Society 副编辑、IEEE Microwave Magazine 特邀编辑等;兼任 IEEE IMS 技术分委会主席,兼任/曾任 ISSCC、EuMW、RFIC、CICC 技术委员会委员等。

#### **TALK**

#### **RFIC: Amplifiers and Array-System**

This presentation will firstly focus on the power amplifier (PA) and array-system requirements of 5G-Advanced (5G-A) RFICs. Then, the on-chip fast self-calibration switched-capacitor PA and wideband digital-RF phased-array transceiver using conventional CMOS technology will be discussed.

**WORKSHOP ON IC ADVANCES IN CHINA**

洪志良

2025年3月27日・第2天

大宴会厅 2

Talk #3.1 / 08:30-08:55

### 复旦大学

洪志良,瑞士苏黎世高等理工学院博士,复旦大学教授,博导。

#### **TALK**

### **Energy Efficiency is the key in PMU and PA design**

Whether use new architecture or innovel circuit technique, PMU and PA designers will pay the energy efficiency in the first! This presentation will introduce our two works, "A Fully Integrated Digital Polar Transmitter With Single-Ended Doherty PA and DLL-Based Three-Segment Hybrid DTC in 28 nm CMOS" and "A 94.4% Peak Efficiency Coupled-Inductor Hybrid Step-Up Converter With Load-Independent Output Voltage Ripple", published in JSSC 2024.

**WORKSHOP ON IC ADVANCES IN CHINA**

黄沫

# 2025年3月27日・第2天 大宴会厅2

Talk #3.2 / 08:55-09:20

### 澳门大学

于 2005, 2008, 2014 年分别在中山大学微电子学与固体电子学专业获得本科,硕士,博士学位。2008 至 2014 年,在广晟微电子有限公司,作为项目经理参与了 TD-LTE,TD-SCDMA 等多款商用芯片的研发设计。2014 年 12 月至 2016 年 9 月,在澳门大学 AMSV 国家重点实验室任博士后。2016 年 10 月至 2019 年 8 月,在华南理工大学电子与信息学院,任副教授。2019 年 9 月至今,加入澳门大学 AMSV 国家重点实验室,任助理教授。主要研究方向为电源管理和能量 IC 设计。获授权 23 项中国发明专利,2 项美国专利。黄沫博士获得了 ISSCC 2017 菅野卓雄远东杰出论文奖(中国大陆和港澳地区首次)。指导的博士生获得 2024 SSCS 博士成就奖。现担任 ISSCC 和 CICC 的 TPC 成员,以及 JoS,MEJ 的副主编。

#### **TALK**

#### **Multi-phase Hybrid DC-DC Converters**

This report presents the design methodology of a multi-phase hybrid converters with inherent inductor current balancing, together with fast transient response and wide VCR range.

**WORKSHOP ON IC ADVANCES IN CHINA**

2025年3月27日・第2天 大宴会厅2

Talk #3.3 / 09:20-09:45

屈万园

### 浙江大学

屈万园博士为浙江大学集成电路学院教授、博士生导师、教育部青年长江学者,博士毕业于韩国科学技术院, 2008 年至 2017 年就职于韩国 LG 公司从事集成电路研发工作,历任工程师、资深工程师、责任工程师/项目主管; 2017 年起加入浙江大学并工作至今,长期从事数模混合集成电路设计相关研究工作,主要研究方向为面向三维异构集成的高密度电源管理芯片设计,包括混合电源拓扑的架构构建方法和优化理论、高动态电源环路的控制策略和驱动技术等。

在产业领域,领导量产多款国际领先的高性能电源管理芯片,获授权美国发明专利 9 项、韩国发明专利 5 项、中国发明专利 3 项;在学术领域,发表集成电路设计领域最高水平的国际固态电路会议 ISSCC 和固态电路期刊 JSSC 论文多篇,包括浙江大学为第一单位的首篇 ISSCC 论文,获评国际固态电路会议 2021 年度丝绸之路奖、2022 年度亮点论文。目前担任多个 IEEE 高水平会议技术委员会成员。

#### **TALK**

# A 12A 89.3% Peak Efficiency and 26mV Undershoot 12V/1V Two-Stage Converter with Regulated Resonant Switched-Capacitor Regulators

This work presents a two-stage 12V/1V converter for the vertical power delivery, which adopts a regulated resonant switched-capacitor (RReSC) second stage. The proposed RReSC always operates in the ideal non-regulation mode during steady-state, while maintain voltage regulation during the transients. Therefore, compared with the prior two-stage counterparts, this work shows the best system level efficiency of 89.3% and the best load transient responses with 26mV undershoot under a 4A load step.

**WORKSHOP ON IC ADVANCES IN CHINA**

童志国

2025年3月27日・第2天 大宴会厅2

Talk #3.4 / 09:45-10:10

### 澳门大学

童志国,先后于 2018 年,2021 年,2024 年于天津大学,复旦大学,澳门大学取得学士,硕士,博士学位。现任澳门大学博士后研究员,主要研究方向为应用于高性能计算和人形机器人的电源管理芯片设计;并在集成电路领域顶级会议 ISSCC 和期刊 JSSC 发表 8 篇论文,其中第一作者发表 5 篇(含共一 1 篇)。并获2024-2025 IEEE 固态电路学会博士生成果奖,PwrSoC 2023 最佳学生海报奖等。

#### **TALK**

# HOOP: An Auto-Current-Balanced and Easy-Scalable Hybrid Converters Ring for High Performance Computing

AI is booming. So is the computing power used to train AI models. To satisfy the enormous current demand, the power solution providing large current and high efficiency is strongly required. This work presents an auto-current-balanced and easy-scalable hybrid converters ring structure. It features Hybrid converters with a power ring (O) for current balance and a back ring (O) for phase shedding for computing Power delivery, named as HOOP. By placing the HOOP structure on the backside of the xPU load in a ring configuration, the current can be delivered vertically to the xPUs via short paths, greatly reducing both the on-board and in-package I<sup>2</sup>R losses. Implemented with 180nm BCD process, a maximum current of 16A with four chips is implemented, and a single-chip current density of 1.1A/mm2 is achieved.

**WORKSHOP ON IC ADVANCES IN CHINA**

2025年3月27日 · 第2天 大宴会厅3

Talk #4.1 / 08:30-08:55

### 中国科学院微电子研究所

张锋,中科院微电子所研究员,博士生导师。从事先进集成电路研究二十余年,先后包括主持重点研发计划项目(两项)、863 计划、自然科学基重点项目金等多个国家级课题,参与了十余项国家重大项目的研发,完成了多款芯片的研制开发。在 nature electronics、isscc、JSSC、TCASI 等杂志发表文章 70 余篇。

#### **TALK**

# A 28nm 192.3TFLOPS/W Accurate/Approximate Dual-Mode-Transpose Digital 6T-SRAM CIM Macro for Floating-Point Edge Training and Inference

To address the high energy efficiency requirements for inference and training computations in edge computing, we propose a digitally reconfigurable SRAM in-memory computing macro unit. It supports INT4, INT8 fixed-point formats and FP8, BF16 floating-point formats. It can be configured to operate in approximate or precise computation modes to balance the trade-off between energy efficiency and accuracy. The average energy efficiency for FP8 floating-point operations can reach 192 TFLOPS/W.

**WORKSHOP ON IC ADVANCES IN CHINA**

哈亚军

# 2025年3月27日・第2天 大宴会厅3

Talk #4.2 / 08:55-09:20

### 上海科技大学